Rozborka čipsetu Apple A10 Fusion odhalila pokročilou architekturu

Nedávno uvedený iPhone 7 a iPhone 7 Plus je plný novinek, které si zaslouží zvýšenou pozornost. Pokud vynecháme absenci 3,5mm audio konektoru a voděodolnou konstrukci, tak nejzásadnějším prvkem je u obou modelů zbrusu nový čipset. Apple jej nazývá A10 Fusion a podle aktuálních testů výkonu jde o polovodičovou bestii, která ukazuje záda veškeré konkurenci. Redakce serveru Chipworks tradičně nelenila a SoC podrobila bližšímu zkoumání, čímž odpověděla na řadu zajímavých otázek. Plocha čipsetu zabírá 125 čtverečních milimetrů, přičemž veškerá produkce pochází z továren společnosti TSMC.

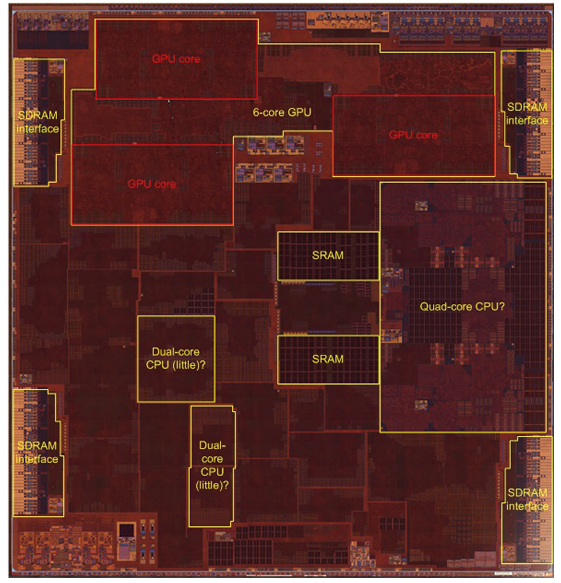

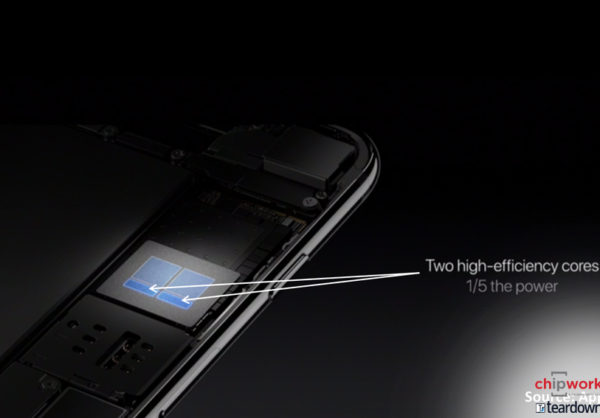

Apple A10 Fusion je nezvykle tenký, za což může speciální technologický postup, který TSMC používá pouze pro výrobu zadanou kalifornským výrobcem. Na přiloženém snímku je zachycena varianta určená pro iPhone 7 s 2GB RAM (LPDDR4), větší iPhone 7 Plus nabízí 3 GB operační paměti. V kontextu s výkonem zaujme 16nm architektura založená na výrobních procesu FinFET. Ačkoli rentgen odhalil vnitřní rozložení, nikomu se zatím nepodařilo s jistotou rozklíčovat funkce jednotlivých oblastí.

Již v prvním pohledu je patrná komplikovanost čipsetu, který se chlubí více než 3 miliardami tranzistorů. Co se týče flash pamětí (15 nm), Apple se rozhodl pro výrobce Hynix a Toshiba s totožnou jakostí kvality. V konečném důsledku lze A10 Fusion označit za velmi pokročilý typ čipsetu určený pro mobilní zařízení. Vývojáři udělali velký kus práce, díky čemuž se může iPhone 7 a iPhone 7 Plus právem pyšnit titulem nejvýkonnějšího smartphonu na trhu.

A10 Fusion na architektuře big.little, kterou má Samsung již třetím rokem, veliký kus práce, to jistě. 😀

Ano, máte pravdu, že jde o architekturu, kterou Samsung používá u řady Exynos, ovšem v tomto případě jde o naprosto unikátní rozvržení (viz. přiložený obrázek), které TSMC tiskne wafery určené pro produkci A10.

Stejně “naprosto unikátní” rozvržení (viz. přiložený obrázek) má každý SoC, viz Google search. 🙂

S tím nesouhlasím. Pro podrobnější informace zkuste navštívit zdroj, ze kterého jsem čerpal. Rozvržení čipsetu se poměrně dost liší od zbytku konvenční ARM produkce… Návrh celé sady si dělal Apple sám.

Apple nechává všechny své SoC vyvíjet podle vlastního návrhu pod licencí od ARM.

Jestliže trváte na tom, že je to “unikátní” návrh pak mi řekněte v čem podstatném se liší od těchto návrhů: http://i.imgur.com/meR6Xwm.png http://i.imgur.com/yc74nA7.jpg

Ono totiž v tom originálním článku sami píšou, že neví, kde jsou jednotlivé komponenty rozmístěny v návrhu SoC, mně se na tom jejich nákresu nezdá umístění méně výkonných jader.

Jistě v rámci iPhonů je A10 “unikátní” protože poprvé využívá big.little,a poprvé má 4xCPU cores v kombinaci s 6xGPU, v minulosti měly SoC v iPhone vždy jen jedno nebo dvě hloupější a energeticky neúsporná jádra. iPad měl jeden z modelů již dříve 3xCPU jádro (to mi přijde mnohem unikátnější), lichý počet jader má málokdo, s vyjímkou SingleCore SoC, a iPadPro má 12xGPU cores, další příklad, který je mnohem více unikátní, protože k takovému řetězení jader, když sečtete jednotlivá jádra ve schématech A9, A9X nebo A10Fusion, tak lehce dojdete k tomu, že většina konkurenčních telefonů na trhu má daleko méně CPU clusterů a GPU clusterů dohromady. Jedinou vyjímkou jsou některá Helia od MTK, ty mají v celkovém počtu o dvě jádra víc (+4xCPU -2xGPU).

A10 Fusion device-level performance boost from 20nm planar to 16FF FinFET vs Snap820/821 14 nm Samsung FinFET LPP, ARMv8-A.

V z toho lze odvodit, že A10 Fusion je podobný chip jako první big.little Exynos5430 (čtyři roky starý návrh), z pohledu energetické úspornosti. Samozřejmě s vyšším SC i MC výkonem na úrovni dnešních Snp820. A10F je 64bit a má rychlejší paměti, stejně jako všechny ostatní moderní SoC.

Méně nm nemusí být vždycky více, jak dokázaly rozdíly mezi loňskými A9 od Samsungu a TSMC, jsem zastáncem toho, že než spěchat v krátkodobém horizontu za nm, je lepší si trochu počkat, než je nižší výrobní proces vychytaný.

The A10 features an Apple-designed 64-bit 2.34 GHz CPU, with a die area of 125 mm2, and is built on TSMC’s 16 nm FinFETprocess [6][7] and is called APL1W24. It’s packaged in a new InFO packaging from TSMC which reduces the height of the package. In the same package there are four Samsung LPDDR4 RAM chips integrating 2 GB of RAM in the iPhone 7, or 3 GB in the iPhone 7 Plus.[6][7] and is about 125 mm2 large. The A10 has a per-high-speed-core L1 cache of 64 KB for data and 64 KB for instructions, an L2 cache of 3 MB shared by both cores, and a 4 MB L3 cache that services the entire SoC

Snap jsem línej opisovat: https://en.wikipedia.org/wiki/List_of_Qualcomm_Snapdragon_devices#Snapdragon_820_and_821